Inhaltsverzeichnis

Pofo Hauptspeichererweiterung 512k

Mit nur einem SRAM

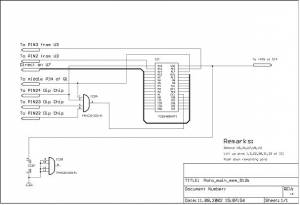

Die Ausführung der Hauptspeichererweiterung erfolgt hier im Gegensatz zu den verbreiteten Methoden nicht mittels vier 128k Chips sondern mit einem einzelnen 512k*8 SRAM der Firma Toshiba. Die Vorteile liegen im geringen Platzbedarf (Chip wird an Stelle von U7 aufgelötet). Der verbleibende Raum kann für ein internes Laufwerk B mit 512k/1M und Backup Batterie genutzt werden (Die Dekodierlogik entspricht der des PCMCIA Adapters).

Ausführung

- Entlöten der Chips

- U5,

- U6,

- U7,

- U8,

- U11.

- Auflöten von

- IC1 /

- IC2,

- verschalten

Fertig (das war ja einfach).

! Der Pull Up Widerstand an IC1 auf dem Foto entfällt !

Anmerkungen

Bei dem verwendeten SRAM (TC554001AFI), welches von der Firma RS-Components bezogen wurde, handelt es sich um die SOP ² Variante (TSOP war nicht erhältlich), welche ein wenig zu breit für die Pads des Pofos ist. Abhilfe wird dadurch geschaffen, dass die Pins, welche direkt mit den Pads von U7 verlötet werden, mit einem kleinen Schraubendreher direkt an die Gehäuseunterseite des Chips gebogen werden. Das Ganze sieht dann in etwa aus wie ein PLCC ² Chip. Die verbleibenden Pins werden leicht nach oben gebogen und mit Fädeldraht laut Schaltplan verschaltet. Der HC21 kann rücklings auf die Platine geklebt und verschaltet werden.

Bei dem verwendeten SRAM (TC554001AFI), welches von der Firma RS-Components bezogen wurde, handelt es sich um die SOP ² Variante (TSOP war nicht erhältlich), welche ein wenig zu breit für die Pads des Pofos ist. Abhilfe wird dadurch geschaffen, dass die Pins, welche direkt mit den Pads von U7 verlötet werden, mit einem kleinen Schraubendreher direkt an die Gehäuseunterseite des Chips gebogen werden. Das Ganze sieht dann in etwa aus wie ein PLCC ² Chip. Die verbleibenden Pins werden leicht nach oben gebogen und mit Fädeldraht laut Schaltplan verschaltet. Der HC21 kann rücklings auf die Platine geklebt und verschaltet werden.

Eine Abkopplung des CE/ - Signals mittels Transistor macht meines Erachtens wenig Sinn, da alle an den HC21 geführten Signale im Standby auf High gehen, welches ein High an CE\ zur Folge hat (Standby RAM). Die Stromaufnahme des Pofos bewegt sich wie beim Original im Standby bei ca. 250 ²300µA. Wer sich Stress beim Batteriewechsel (sollte binnen 10s durchgeführt werden) ersparen will, kann die Speicherkondensatoren C14/15 durch Parallelschaltung mit geeigneten Typen vergrößern oder durch Goldcaps ersetzen.

Bezugsquellen

Bauteillieferant RS ² Components, Bauteilbezeichnung TC554001AF7L(Y), Preis 12,81 + MWST. www.rsonline.de